Моделирование работы процессора — Документ

Информатика, 11 класс К.Ю. Поляков, Е.А. Еремин

Моделирование

Практические работы

-

Моделирование работы процессора

Напишите программу, которая моделирует работу процессора. Процессор имеет 4 регистра, они обозначаются R0, R1, R2 и R3. Все команды состоят из трех десятичных цифр: код операции, номер первого регистра и номер второго регистра (или число от 0 до 9). Коды команд и примеры их использования приведены в таблице:

Код операции | Описание | Пример | Псевдокод |

1 | запись константы | 128 | R2 := 8 |

2 | копирование значения | 203 | R3 := R0 |

3 | сложение | 331 | R1 := R1 + R3 |

4 | вычитание | 431 | R1 := R1 – R3 |

Обратите внимание, что результат

записывается во второй регистр. Команды вводятся последовательно как

символьные строки. После ввода каждой

строки программа показывает значения

всех регистров.

Команды вводятся последовательно как

символьные строки. После ввода каждой

строки программа показывает значения

всех регистров.

*Добавьте в систему команд умножение, деление и логические операции c регистрами – «И», «ИЛИ», «исключающее ИЛИ».

*Добавьте в систему команд логическую операцию «НЕ». Подумайте, как можно использовать второй регистр.

*Сделайте так, чтобы в команде с кодом 1 можно было использовать шестнадцатеричные значения констант (0-9, A-F).

Добавьте обработку ошибок типа «неверная команда», «неверный номер регистра», «деление на ноль».

**Подумайте, как можно было бы организовать условный переход: перейти на N байт вперед (или назад), если результат последней операции – ноль.

Моделирование движения

Парашютист массой 90 кг разгоняется в свободном падении до скорости 10 м/с и на высоте 50 м раскрывает парашют, площадь которого 55 м2. Коэффициент сопротивления парашюта равен 0,9. Выполните следующие задания:

постройте графики изменения скорости и высоты полета в течение первых 4 секунд;

-

определите, с какой скоростью приземлится парашютист?

сравните результаты моделирования с установившимся значением скорости, вычисленным теоретически.

теоретически | моделирование | |

Скорость приземления, м/с |

Напишите программу, которая моделирует полет мяча, брошенного вертикально вверх, при

мм,

г,

м/с,

с.

Остальные необходимые данные есть в тексте § 9. Выполните следующие задания:

вычислите время полета и максимальную высоту подъема мяча, используя модель движения без сопротивления воздуха:

сравните эти результаты с полученными при моделировании с учетом сопротивления;

без учёта сопротивления

с учётом сопротивления

Время полета, с

Максимальная высота, м

Скорость приземления, м/с

можно ли в этой задаче пренебречь сопротивлением воздуха? почему?

Ответ:

с помощью табличного процессора постройте траекторию движения мяча, а также графики изменения скорости, ускорения и силы сопротивления;

уменьшите шаг до 0,01 с и повторите моделирование; сделайте выводы по поводу выбора шага в данной задаче.

Ответ:

*Выполните моделирование движения мяча, брошенного под углом 45° к горизонту:

определите время полета, максимальную высоту и дальность полета мяча, скорость в момент приземления;

без учёта сопротивления

с учётом сопротивления

Время полета, с

Максимальная высота, м

Дальность полета, м

Скорость приземления, м/с

- сравните результаты со случаем, когда

сопротивление воздуха не учитывается;

сделайте выводы.

Ответ:

Моделирование популяции животных

Для выполнения работы откройте файл-заготовку Популяция.xls.

Постройте графики изменения численности популяции животных для моделей ограниченного и неограниченного роста при , и в течение первых 15 периодов. Определите, когда модель неограниченного роста перестает быть адекватной (отклонение от модели ограниченного роста составляет более 10%).

Ответ:

Используя подбор параметра, определите, при каких коэффициентах модель неограниченного роста остается адекватной в течение не менее 10 периодов.

Ответ:

Используя модель ограниченного роста из предыдущей задачи, выполните моделирование популяции с учетом отлова (). Предполагается, что животных начали отлавливать через 10 лет после начала наблюдений.

постройте график изменения численности животных;

определите количество животных в состоянии равновесия по результатам моделирования; зависит ли оно от начальной численности?

Ответ:

определите количество животных в состоянии равновесия теоретически, из модели ограниченного роста с отловом; сравните это значение с результатами моделирования

Ответ:

Ответ:

Ответ:

*определите максимально допустимый отлов теоретически, из модели ограниченного роста с отловом; сравните это значение с результатами моделирования

Ответ:

Моделирование эпидемии

Для выполнения работы откройте

файл-заготовку Эпидемия. xls.

xls.

При эпидемии гриппа число больных изменяется по формуле

,

где – количество заболевших в -й день, а – количество выздоровевших в тот же день. Число заболевших рассчитывается согласно модели ограниченного роста:

,

где – общая численность жителей, – коэффициент роста и – число переболевших (тех, кто уже переболел и выздоровел, и поэтому больше не заболеет):

.

Считается, что в начале эпидемии заболел 1 человек, все заболевшие выздоравливают через 7 дней и больше не болеют.

Выполните моделирование развития эпидемии при и до того момента, когда количество больных станет равно нулю. Постройте график изменения количества больных.

Ответьте на следующие вопросы:

Когда закончится эпидемия?

Ответ:

Сколько человек переболеет, а сколько вообще не заболеет гриппом?

Ответ:

Каково максимальное число больных в один день?

Ответ:

Изменяя коэффициент , определите, при каких значениях модель явно перестает быть адекватной.

Ответ:

*Сравните модель, использованную в этой работе, со следующей моделью:

, .

Анализируя результаты моделирования, докажите, что эта модель неадекватна. Какие допущения, на ваш взгляд, были сделаны неверно при разработке этой модели?

Ответ:

Сравните поведение двух моделей при , и . Сделайте выводы.

Ответ:

Модель «хищник-жертва»

Для выполнения работы откройте

файл-заготовку ХищникЖертва. xls.

xls.

Выполните моделирование биологической системы «щуки-караси»

где – численность карасей

– численность щук

при следующих значениях параметров:

– коэффициент прироста карасей;

– предельная численность карасей;

– начальная численность карасей;

– начальная численность щук;

– коэффициент смертности щук без пищи;

и – коэффициенты модели.

Постройте на одном поле графики изменения численности карасей и щук в течение 30 периодов моделирования.

Ответьте на следующие вопросы:

Сколько карасей и щук живут в водоеме в состоянии равновесия?

Ответ:

Что влияет на количество рыб в состоянии равновесия: начальная численность хищников и жертв или значения коэффициентов модели?

Ответ:

На что влияет начальная численность хищников и жертв?

Ответ:

Подберите значения коэффициентов, при которых модель становится неадекватна.

Ответ:

Подберите значения коэффициентов, при которых щуки вымирают, а численность карасей достигает предельно возможного значения. Как вы можете объяснить это с точки зрения биологии?

Ответ:

Практическая работа № 10а.

Модель «две популяции»

Для выполнения работы откройте файл-заготовку ДвеПопуляции.xls.

Белки и бурундуки живут в одном лесу и

едят примерно одно и то же (конкурируют

за пищу). Модель, описывающая изменение

численности двух популяций, имеет вид:

Модель, описывающая изменение

численности двух популяций, имеет вид:

Здесь и – численность белок и бурундуков; и – их максимальные численности; и – коэффициенты прироста; и – коэффициенты взаимного влияния.

Объясните, на основании каких предположений была построена эта модель.

Ответ:

Выполните моделирование изменения численности двух популяций в течение 15 периодов при , , , , и . Постройте графики изменения численности обеих популяций на одном поле.

Ответьте на следующие вопросы:

Является ли эта модель системной? Почему?

Ответ:

Какова численность белок и бурундуков в состоянии равновесия?

Ответ:

Что влияет на состояние равновесия?

Ответ:

На что влияет начальная численность животных?

Ответ:

При каком значении коэффициента бурундуки вымрут через 25 лет? (используйте подбор параметра).

Ответ:

Найдите какие-нибудь значения коэффициентов, при которых модель становится неадекватна;

Ответ:

Предложите аналогичную модель взаимного влияния трех видов.

Ответ:

Саморегуляция

Для выполнения работы откройте файл-заготовку Саморегуляция.xls.

Биологи выяснили, что для каждого вида

животных существует некоторая минимальная

численность популяции, которая необходима

для выживания этой колонии. Это может

быть одна пара животных (например, для

ондатр) или даже тысячи особей (для

американских почтовых голубей). Если

количество животных становится меньше

этого минимального значения, популяция

вымирает. Для этого случая предложена

следующая модель изменения численности:

Это может

быть одна пара животных (например, для

ондатр) или даже тысячи особей (для

американских почтовых голубей). Если

количество животных становится меньше

этого минимального значения, популяция

вымирает. Для этого случая предложена

следующая модель изменения численности:

, (*)

Эта модель отличатся от модели ограниченного роста только дополнительным множителем , где и – некоторые числа (параметры), смысл которых вам предстоит выяснить.

Выполните моделирование для 30 периодов при следующих значениях параметров модели:

Сравните результаты, которые дают модель классическая модель ограниченного роста и модель (*). Сделайте выводы и опишите, в чём проявляется саморегуляция для этих моделей.

Ответ:

Постепенно увеличивая коэффициент от 0 до 500, выясните с помощью моделирования, как влияет этот коэффициент на саморегуляцию.

Ответ:

Через 10 периодов в результате изменения природных условия число животных уменьшилось до 400 (то есть, ). Выполните моделирование при этих условиях и опишите, как работает саморегуляция и чем отличается поведение двух сравниваемых моделей.

Ответ:

Повторите моделирование п. 3 при и сделайте аналогичные выводы:

Ответ:

Экспериментируя с моделями, найдите минимальную численность популяции , при которой она выживает в соответствии с моделью (*).

Ответ:

Сделайте выводы о смысле коэффициента в модели (*).

Ответ:

Сравните свойства саморегуляции для модели ограниченного роста и модели (*).

Ответ:

Моделирование работы банка

Для моделирования обслуживания клиентов в банке предложена следующая модель:

где – количество клиентов, вошедших за -ую минуту, а – количество клиентов, обслуженных за это время;

достаточным считается число касс, при которых среднее время ожидания превышает установленный предел не более, чем 5% рабочего времени в течение дня.

Используя эту вероятностную модель работы банка, напишите программу, с помощью которой определите минимальное необходимое количество касс при следующих исходных данных:

, , , .

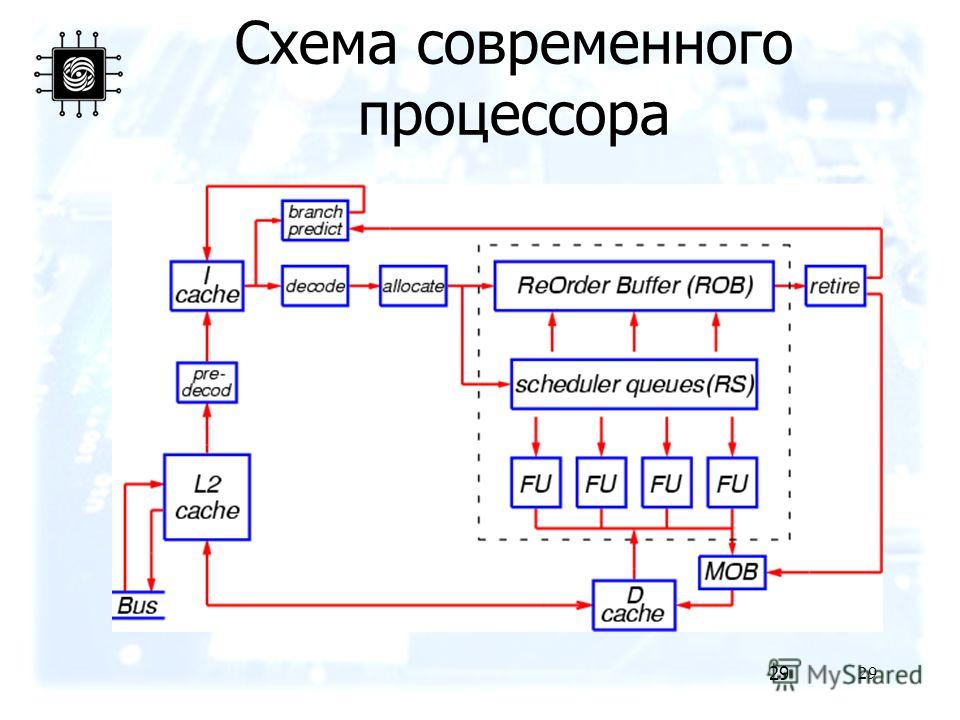

Интерфейс программы «Моделирование работы процессора»

регистре команд хранится предыдущая команда (ADD [0]), в регистре адреса – адрес её операнда [0], в регистре данных и аккумуляторе – значение этого операнда (53) и в счётчике команд – адрес рассматриваемой команды [5].

2.Адрес команды пересылается из программного счётчика в регистр адреса: У7, У1. Надо отметить, что в базовой ЭВМ все пересылки между регистрами выполняются через арифметико-логическое устройство.

3.Из памяти (по команде устройства управления) выбирается содержимое ячейки памяти, адрес которой расположен в регистре адреса и производится увеличение на единицу содержимого счётчика команд: У2, У7, тип операции для АЛУ: увеличение на 1, команда чтения из памяти.

4.Следующий такт – пересылка нового значения в программный счётчик: У8.

5.Содержимое регистра данных пересылается в регистр команд, и устройство управления начинает декодировать команду: У4, У6.

6.Перечисленные действия относятся к «Выборке команды».

7.Расшифровав код операции командыADD [1], устройство управления пересылает её адресную часть(адрес 1) в регистр адреса: У4, У1. Пересылка осуществляется из регистра данных, где ещё сохранилась копия команды.

Пересылка осуществляется из регистра данных, где ещё сохранилась копия команды.

8.Из памяти в регистр данных считывается содержимое ячейки памяти, адрес которой расположен в регистре адреса: У2, команда чтения из памяти.

9.Выполняется операция сложения содержимого регистра данных и аккумулятора: У4, У10, тип операции для АЛУ: сложение операндов.

10.Полученная в арифметико-логическом устройстве сумма пересылается в аккумулятор: У9.

11.Исполнение команды завершено.

Программа служит для моделирования работы процессора при исполнении программы пользователя, набранной в памяти ЭВМ.

Программа «Моделирование работы процессора» рассчитана на запуск на ЭВМ с разрешением экрана не менее 1024 х 768.

9

Запуск программы выполняется выбором команды в меню Пуск.

Пуск \ Программы \ Моделирование работы процессора

После запуска программы на экране появляется главное окнопро граммы (Рис. 4), которое содержит мнемосхему базовой ЭВМ. На мнемосхеме отображается текущие значения всех регистров процессора, а также фрагмент несколько ячеек области памяти.

Пользователь имеет возможность набрать свою программу на языке машинных инструкций и выполнить её в пошаговом режиме на базовой ЭВМ.

Рис. 4. Главное окно программы «Моделирование работы процессора»

2. Окно редактирования (Рис. 5) текста программы вызывается с помощью команды меню программы Программа \ Изменить, или по двойному щелчку мышью по таблице «Память» в главном окне программы.

10

Адрес загружается в ПС перед запуском программы

Указать тип данных, добавляемых в ячейку памяти

Выбранная ячейка памяти

Добавить

сформированную команду или число в выбранную ячейку памяти

Очистить выбранную ячейку памяти

Рис. 5. Окно редактирования программы

3.Программа пользователя может исполняться либо непрерывно, либо

состановом после выполнения каждой микрокоманды. Настройка режима исполнения программы пользователя(непрерывно или по усмотрению) осуществляется с помощью окна«Настройка», которое вызывается по ко-

манде Программа \ Настройка.

4. Управление запуском, остановом и поэтапным исполнением осуществляется с помощью кнопок панели управления в левой нижней части главного окна программы (Рис. 6).

Вызов окна редактирования программы пользователя Начать выполнения программы пользователя Переход к исполнению следующей микрокоманды Остановить выполнение программы пользователя

Вызов окна «Настройка» Помощь Выход из программы «Моделирование работы процессора»

Рис. 6. Панель управления программой

11

5. Программа пользователя может быть сохранена в файле данных и загружена вновь с помощью команд меню Файл.

Задание для самостоятельного выполнения

1.Набрать программу сложения двух чисел (табл. 2) и изучить работу базовой ЭВМ на примере выполнения данной программы.

2.Разработать программу, выполняющую следующие действия:

№ | программа | Хранение операндов и ре- |

|

| зультатов |

1 | y = a–(b+c) | До программы |

| z = a AND d |

|

2 | y = (a–b)+c+d | После программы |

| z = a OR 2d |

|

3 | y = a AND b+c | До программы |

| z = b |

|

4 | y = a AND b+c | После программы |

| z = b+c |

|

5 | y = a OR b+c | До программы |

| z = b-c |

|

6 | y = a AND b-a+d | После программы |

| z = (b+c) OR a |

|

7 | y = a AND b OR a | До программы |

| z = b-c |

|

|

|

|

8 | y = a-(b AND c) | После программы |

| z = 2b+c |

|

9 | y = a-(b AND c) | До программы |

| z = c+b |

|

|

|

|

10 | y = a OR (b AND c) | После программы |

| z = 2c AND d |

|

11 | y = a AND c | До программы |

| z = 2y+3b |

|

12 | y = (a AND c) OR a | После программы |

| z = 2b-c |

|

13 | y = a+(b OR c) | До программы |

| z = (b+2c) AND d |

|

14 | y = a OR b+a | После программы |

| z = b-c+d |

|

12

Моделирование центрального процессора с помощью интерпретации

Двоичная трансляция и симуляция

Двоичная трансляция и симуляция 28. 10.2013 [email protected] Григорий Речистов [email protected] Статическая ДТ Динамическая ДТ Проблемы и решения 2 Вопросы к прошлой лекции 1. Определение процесса

10.2013 [email protected] Григорий Речистов [email protected] Статическая ДТ Динамическая ДТ Проблемы и решения 2 Вопросы к прошлой лекции 1. Определение процесса

2014 МГУ/ВМК/СП. Лекция февраля

Лекция 2 12 февраля Архитектура фон Неймана mov eax, ecx mov eax, dword [0x2014] add eax, 0xff 1. Двоичное кодирование информации 2. Неразличимость команд и данных Вспоминаем Си-машину 3. Адресуемость

ПодробнееСимуляция, управляемая событиями

Курс «Программное моделирование вычислительных систем» Григорий Речистов [email protected] 6 апреля 2015 г. 1 Таймер 2 Отложенный ответ 3 Теория 4 Практический пример 5 Косимуляция 6 Практический

ПодробнееЛекция 7. Интерпретаторы и компиляторы

Лекция 7. Интерпретаторы и компиляторы Абстрактные машины и реальные процессоры Язык программирования машинный код некоторого абстрактного компьютера, отличающегося от реальных процессоров. Цель трансляции

ПодробнееОсновы программного конструирования

Лектор: А.Д.Хапугин Основы программного конструирования Лекция 5. Общие понятия архитектур ЭВМ — продолжение (начало см. в лекциях 3 и 4) Материалы доступны в Интернете по адресу: http://www.excelsior.ru/afti/

Подробнее2017 МГУ/ВМК/СП. Лекция февраля

Лекция 5 22 февраля Организация вызова функций Вопросы Передача управления и возвращение обратно Вычисление значений фактических параметров и их размещение Передача возвращаемого значения Размещение автоматических

Подробнее2019 МГУ/ВМК/СП. Лекция февраля

Лекция 5 27 февраля Организация вызова функций Вопросы Передача управления и возвращение обратно Вычисление значений фактических параметров и их размещение Передача возвращаемого значения Размещение автоматических

ПодробнееРаспределение памяти

Распределение памяти Распределение памяти — это процесс, в результате которого отдельным элементам исходной программы ставятся в соответствие адрес, размер и атрибуты области памяти, необходимой для размещения

ПодробнееЯзыки программирования

3. Влияние архитектуры Структура компьютера 1. Данные; 2. Элементарные операции; 3. Управление последовательностью действий; 4. Доступ к данным; 5. Управление памятью; 6. Операционная среда. 2 Данные Хранение:

Влияние архитектуры Структура компьютера 1. Данные; 2. Элементарные операции; 3. Управление последовательностью действий; 4. Доступ к данным; 5. Управление памятью; 6. Операционная среда. 2 Данные Хранение:

1 ФУПМ 2-й семестр. Домашние задания.

1 ФУПМ 2-й семестр. Домашние задания. Первое задание. Требуется реализовать эмулятор компьютера FUMP2 с заданной архитектурой. FUPM2 есть машина с архитектурой Фон-Неймана с адресным пространством в 2

ПодробнееГенератор тестовых программ

RISC-V Developers Forum 7 декабря, Москва Генератор тестовых программ MicroTESK for RISC-V Андрей Татарников Институт системного программирования им. В.П. Иванникова Российской академии наук Введение Тестирование

ПодробнееВведение в информатику

Введение в информатику Е. А. Яревский физический факультет СПбГУ 2018 ЛЕКЦИЯ 7 Архитектура и устройство компьютера Расширения архитектуры фон-неймана Принципы фон Неймана Принцип двоичного кодирования

Подробнее2017 МГУ/ВМК/СП. Лекция A. 15 марта

Лекция A 15 марта Оптимизация доступа к элементам массива a j-ый столбец #define N 16 typedef int fix_matrix[n][n]; Вычисления Проход по всем элементам в столбце j Оптимизация Выборка последовательных

ПодробнееПрактикум (лабораторный). Дополнение 1

Практикум (лабораторный). Дополнение 1 Лабораторная работа 1. Представление информации 3.3.Преобразование дробной части десятичного числа Преобразование дробной части выполняется за счет умножения на основание

Подробнее2019 МГУ/ВМК/СП. Лекция 0xA. 16 марта

Лекция 0xA 16 марта Матрица N X N Фиксированные размерности Значение N известно во время компиляции Динамически задаваемая размерность. Требуется явное преобразование индексов Традиционный способ реализации

Требуется явное преобразование индексов Традиционный способ реализации

Джон фон Нейман ( )

Джон фон Нейман (1903-1957) Архитектура Джона фон Неймана Кодирование двоичным кодом. Переход на двоичную логику позволил использовать хорошо разработанный к тому моменту аппарат алгебры логики для анализа

ПодробнееИ.В. Музылёва, 2015 Страница 1

Тема 12 Составление линейных программ и их оформление Теория Линейными называются программы, состоящие из команд, выполняемых одна за другой, без переходов и подпрограмм. Примечания: 1) В учебном стенде

ПодробнееКЛАССИФИКАЦИЯ ROP ГАДЖЕТОВ

КЛАССИФИКАЦИЯ ROP ГАДЖЕТОВ Алексей Вишняков [email protected] Москва, 02 декабря 2016 г. Актуальность В современных программах могут присутствовать тысячи программных дефектов Техника возвратно-ориентированного

Подробнее2015 МГУ/ВМК/СП. Лекция февраля

Лекция 5 21 февраля Далее Архитектура фон Неймана Архитектура IA-32 Вычисление арифметических выражений Передача управления Организация вызова функций 2 Организация вызова функций Вопросы Передача управления

ПодробнееРаспределение памяти

Распределение памяти Распределение памяти — это процесс, в результате которого отдельным элементам исходной программы ставятся в соответствие адрес, размер и атрибуты области памяти, необходимой для размещения

ПодробнееВиртуализация. Антоненко Виталий

Виртуализация Антоненко Виталий Виртуализация «на пальцах» Виртуализация компьютера означает, что можно заставить компьютер казаться сразу несколькими компьютерами одновременно или совершенно другим компьютером.

Лекция 5. Центральный микропроцессор

Лекция 5 Центральный микропроцессор Архитектура ПЛК 2 Под архитектурой микроконтроллера понимают комплекс его аппаратных и программных средств, предоставляемых пользователю. Основные модули ПЛК: центральный

Подробнее2014 МГУ/ВМК/СП. Лекция марта

Лекция 11 19 марта Как сохранить место Размещаем большие типы первыми struct S4 { char c; int i; char d; } *p; struct S5 { int i; char c; char d; } *p; Результат (K=4) c 3 байта i d 3 байта i c d 2 байта

ПодробнееЛекция 5. Анализ быстродействия программ

Название Лекция 5. Анализ быстродействия программ Инструменты разработки быстрых программ 2 января 2016 г. Лекция 5 1 / 21 Виды инструментов Методы измерения производительности программ Виды анализа Принцип

Подробнее2017 МГУ/ВМК/СП. Лекция D. 25 марта

Лекция D 25 марта Какие есть компиляторы и соглашения о вызове функций? 2017 МГУ/ВМК/СП Компиляторы LLVM clang (open source) GNU gcc (open source) Microsoft Visual Studio vc Intel icc еще компиляторы PGI

ПодробнееОсновные функции микропроцессора :

Архитектура МП Основные понятия Микропроцессор — это программно-управляемое устройство, предназначенное для обработки цифровой информации и управления процессами этой обработки, выполненной в виде одной

Подробнее2018 МГУ/ВМК/СП. Лекция 0xA. 14 марта

Лекция 0xA 14 марта zip_dig cmu = { 1, 5, 2, 1, 3 ; zip_dig mit = { 0, 2, 1, 3, 9 ; zip_dig ucb = { 9, 4, 7, 2, 0 ; #define UCOUNT 3 int *univ[ucount] = {mit, cmu, ucb; Переменная univ представляет собой

Подробнее2016 МГУ/ВМК/СП.

Лекция 0xB. 16 марта

Лекция 0xB. 16 мартаЛекция 0xB 16 марта Выполнение правил выравнивания для полей Внутри структуры Выравнивание должно выполняться для каждого поля Размещение всей структуры Для каждой структуры определятся требование по выравниванию

ПодробнееМашинное представление чисел

Машинное представление чисел Целые числа Беззнаковые числа В современных ЭВМ для представления чисел используется двоичная система счисления. При использовании для представления положительных целых чисел

ПодробнееЦифровые сигнальные процессоры TMS320C674x

Основы программирования цифровых сигнальных процессоров Цифровые сигнальные процессоры TMS320C674x Конспект лекций РГРТУ, 2018 Лекция 2. Архитектура ЦСП операционное ядро По фон-нейману электронно-вычислительная

ПодробнееРазделитель программ для записи в ППЗУ

Разделитель программ для записи в ППЗУ 5 5.1. Введение Программа разделителя программ выделяет ПЗУ части из выходного.exe файла редактора связей и формирует информацию для использования программаторами

ПодробнееГлава 4. Форматы команд и данных

Глава 4. Форматы команд и данных В этой главе вводятся основные определения и рассматриваются важные базовые понятия, которые будут необходимы для дальнейшего изучения архитектуры ЭВМ. С этой целью будут

ПодробнееТ О Ч Н О С Т Ь — О С Н О В А Д О В Е Р И Я

Т О Ч Н О С Т Ь — О С Н О В А Д О В Е Р И Я Измерение ИМС памяти при помощи тестера FORMULA. Чехович С.Д. Обзор структуры схемы формирования последовательности тестовых векторов Тестера. Формирование тестовых

ПодробнееЛекция 1.

Языки и трансляторы

Языки и трансляторыЛекция 1 Языки и трансляторы Компьютерные языки Лексика (словарь) Синтаксис (правила построения «предложений») Семантика (смысл «предложений»)! Формализация математическая модель эффективная реализация

ПодробнееМНОГОЯДЕРНАЯ АРХИТЕКТУРА УНИВЕРСАЛЬНОЙ

МНОГОЯДЕРНАЯ АРХИТЕКТУРА УНИВЕРСАЛЬНОЙ 32-ух РАЗРЯДНОЙ УЧЕБНОЙ МАШИНЫ Семенов А. А. Московский государственный институт радиотехники, электроники и автоматики (технический университет) Универсальная 32х

ПодробнееВычислительный конвейер

Вычислительный конвейер Pipeline http://arkov.narod.ru В.Арьков 1 Производственный конвейер Assembly line Поточная организация производства постепенная сборка и механическое перемещение изделия от одного

ПодробнееВведение в информатику

Введение в информатику Е.А.Яревский физический факультет СПбГУ 2016 Лекция 5 Архитектура и устройство компьютера История развития ЭВМ 1) 1642-1945 Механические компьютеры 2) 1945-1955 Электронные лампы

Подробнее2019 МГУ/ВМК/СП. Лекция 0xD. 30 марта

Лекция 0xD 30 марта Зачем переходить на 64-х разрядную архитектуру? Особенности полноценной 64-х разрядной процессорной архитектуры АЛУ оперирует 64-х разрядными данными (Большой) набор 64-х разрядных

ПодробнееМоделирование процессора MIPS в Simulink

${form_setting.title_name}

${form_setting.first_name_required}

* ${form_setting.first_name_required} ${form_setting. title_fam}

title_fam}

${form_setting.last_name_required}

* ${form_setting.last_name_required}${form_setting.title_otchestvo}

Для преподавателей отчество обязательно

* Для преподавателей отчество обязательно${form_setting.title_phone}

*${country_title}

${phone.title} ${form_setting.phone_required} ${form_setting.country_required}${form_setting.type_action}

*${action.title}

${form_setting.type_action_required}${form_setting.type_action_required}

${form_setting.title_find_company}

* Выберите организацию Такой организации нет${org.title}

Выберите организацию

Некорректный url сайтаНекорректный url сайта

${form_setting.title_no_company}

${form_setting.title_fac}

${form_setting.facultet_required}

${Data.select_facultet.title}

${faculty.title}

${form_setting.facultet_required}Не нашел в списке Факультет

${form_setting.title_caf}

${form_setting.cafedra_required}

${Data.select_cafedra}

${cafedra.title}

${form_setting.cafedra_required}Не нашел в списке Кафедру

${form_setting.title_position}

${form_setting.position_required}

* ${ error }${form_setting.title_departament}

Реферат по информатике на тему «Процессоры и моделирование работы процессоров»

Муниципальное автономное общеобразовательное учреждение города Калининграда средняя образовательная школа №25 с углубленным изучением отдельных предметов им. И.В. Грачева

Реферат

по теме: «Процессоры и моделирование работы процессора»

Реферат составил:

Ученик 10Б класса

Фисюк Максим

Проверил:

учитель информатики

первой категории

Чернышова И.В.

Калининград

2020 г.

Содержание Стр.

Введение……………………………………………….…………………. 3

1 История развития процессоров…………………….…………………. 4

2 Алгоритм работы процессора……………………….………………… 10

2.1 Устройство процессора…………………….……………………….. 10

2.2 Алгоритм работы процессора…………………………………………………… 11

2.3 Прерывание процессора…………………………………………………………… 12

3 Моделирование работы процессора…………………………………………….. 15

Заключение…………………………………………………………………………………… 17

Список источников…………………………………………………………………… 18

Введение

Одним из основных устройств современного персонального компьютера является центральный процессор. Который, на первый взгляд, просто выращенный по специальной технологии кристалл кремния. Однако этот кристалл содержит в себе множество отдельных элементов – транзисторов, которые в совокупности и наделяют компьютер способностью «думать».

История создания микропроцессора началась еще в 50-х годах, когда на смену электронным лампам пришли компактные «электронные переключатели» — транзисторы, затем – интегральные схемы, в которых впервые удалось объединить на одном кристалле кремния сотни крохотных транзисторов. Но все-таки отсчет летоисчисления компьютерной эры ведут с 1971 года, с момента появления первого микропроцессора.

За три десятка лет, прошедших с этого знаменательного дня, процессоры сильно изменились. Современный процессор — это не просто набор транзисторов, а целая система множества важных устройств.

1 История развития процессоров

В настоящее время существуют много фирм по производству процессоров для персональных компьютеров. Это Intel, AMD, Cyrix, VIA, Centaur/IDT, NexGen, и многие другие. Однако наиболее популярными являются Intel и AMD. Развитие процессоров этих ведущих фирм мы и постараемся рассмотреть.

Однако прежде чем углубляться в историю производства процессоров необходимо дать характеристику некоторым техническим терминам характеризующих процессор.

Тактовая частота – это скорость работы процессора, а именно количество операций выполненных на протяжении 1 секунды.

Поколения – поколения процессоров отличаются друг от друга скоростью работы, архитектурой, исполнением и внешним видом. Если просмотреть поколения процессоров фирмы Intel то их было 8 (8088, 286, 386, 486, Pentium, PentiumII, PentiumIII, PentiumIV).

Модификация –у ведущих и постоянно конкурирующих фирм Intel и AMD есть две модификации процессоров. У Intel это Pentium и Celeron, у AMD это Athlon и Duron. Pentium и Athlon это дорогие процессоры для графических станций или серверов, а Celeron и Duron это процессоры для домашних компьютеров.

Технология производства – под технологией производства в данном случае понимают размер минимальных элементов процессора. Так в 1999 году фирмы перешли на новую, 0,13 – микронную технологию.

КЭШ-память первого уровня – небольшая (несколько десятков килобайт) сверхбыстрая память, предназначенная для хранения промежуточных результатов вычислений.

КЭШ-память второго уровня – эта память более медленная, но она больше от 128 до 512 кбайт.

Центральный процессор (ЦП; также центра́льное процессорное устройство — ЦПУ; англ. centralprocessingunit, CPU, дословно — центральное обрабатывающее устройство, часто просто процессор) — электронный блок либо интегральная схема, исполняющая машинные инструкции (код программ), главная часть аппаратного обеспечения компьютера или программируемого логического контроллера. Иногда называют микропроцессором или просто процессором.

Изначально термин центральное процессорное устройство описывал специализированный класс логических машин, предназначенных для выполнения сложных компьютерных программ. Вследствие довольно точного соответствия этого назначения функциям существовавших в то время компьютерных процессоров он естественным образом был перенесён на сами компьютеры. Начало применения термина и его аббревиатуры по отношению к компьютерным системам было положено в 1960-е годы. Устройство, архитектура и реализация процессоров с тех пор неоднократно менялись, однако их основные исполняемые функции остались теми же, что и прежде.

Главными характеристиками ЦПУ являются: тактовая частота, производительность, энергопотребление, нормы литографического процесса, используемого при производстве (для микропроцессоров), и архитектура.

Ранние ЦП создавались в виде уникальных составных частей для уникальных и даже единственных в своём роде компьютерных систем. Позднее от дорогостоящего способа разработки процессоров, предназначенных для выполнения одной единственной или нескольких узкоспециализированных программ, производители компьютеров перешли к серийному изготовлению типовых классов многоцелевых процессорных устройств. Тенденция к стандартизации компьютерных комплектующих зародилась в эпоху бурного развития полупроводниковых элементов, мейнфреймов и мини-компьютеров, а с появлением интегральных схем она стала ещё более популярной. Создание микросхем позволило ещё больше увеличить сложность ЦП с одновременным уменьшением их физических размеров. Стандартизация и миниатюризация процессоров привели к глубокому проникновению основанных на них цифровых устройств в повседневную жизнь человека. Современные процессоры можно найти не только в таких высокотехнологичных устройствах, как компьютеры, но и в автомобилях, калькуляторах, мобильных телефонах и даже в детских игрушках. Чаще всего они представлены микроконтроллерами, где, помимо вычислительного устройства, на кристалле расположены дополнительные компоненты (память программ и данных, интерфейсы, порты ввода-вывода, таймеры и др.). Современные вычислительные возможности микроконтроллера сравнимы с процессорами персональных ЭВМ десятилетней давности, а чаще даже значительно превосходят их показатели.

История развития производства процессоров полностью соответствует истории развития технологии производства прочих электронных компонентов и схем.

Первым этапом, затронувшим период с 1940-х по конец 1950-х годов, было создание процессоров с использованием электромеханических реле, ферритовых сердечников (устройств памяти) и вакуумных ламп. Они устанавливались в специальные разъёмы на модулях, собранных в стойки. Большое количество таких стоек, соединённых проводниками, в сумме представляло процессор. Отличительными особенностями были низкая надёжность, низкое быстродействие и большое тепловыделение.

Вторым этапом, с середины 1950-х до середины 1960-х, стало внедрение транзисторов. Транзисторы монтировались уже на близкие к современным по виду платы, устанавливавшиеся в стойки. Как и ранее, в среднем процессор состоял из нескольких таких стоек. Возросло быстродействие, повысилась надёжность, уменьшилось энергопотребление.

Третьим этапом, наступившим в середине 1960-х годов, стало использование микросхем. Первоначально использовались микросхемы низкой степени интеграции, содержавшие простые транзисторные и резисторные сборки, затем, по мере развития технологии, стали использоваться микросхемы, реализующие отдельные элементы цифровой схемотехники (сначала элементарные ключи и логические элементы, затем более сложные элементы — элементарные регистры, счётчики, сумматоры), позднее появились микросхемы, содержащие функциональные блоки процессора — микропрограммное устройство, арифметическо-логическое устройство, регистры, устройства работы с шинами данных и команд.

Четвёртым этапом, в начале 1970-х годов, стало создание, благодаря прорыву в технологии, БИС и СБИС (больших и сверхбольших интегральных схем, соответственно), микропроцессора — микросхемы, на кристалле которой физически были расположены все основные элементы и блоки процессора. Фирма Intel в 1971 году создала первый в мире 4-разрядный микропроцессор 4004, предназначенный для использования в микрокалькуляторах. Постепенно практически все процессоры стали выпускаться в формате микропроцессоров. Исключением долгое время оставались только малосерийные процессоры, аппаратно оптимизированные для решения специальных задач (например, суперкомпьютеры или процессоры для решения ряда военных задач) либо процессоры, к которым предъявлялись особые требования по надёжности, быстродействию или защите от электромагнитных импульсов и ионизирующей радиации. Постепенно, с удешевлением и распространением современных технологий, эти процессоры также начинают изготавливаться в формате микропроцессора.

Сейчас слова «микропроцессор» и «процессор» практически стали синонимами, но тогда это было не так, потому что обычные (большие) и микропроцессорные ЭВМ мирно сосуществовали ещё, по крайней мере, 10—15 лет, и только в начале 1980-х годов микропроцессоры вытеснили своих старших собратьев. Тем не менее, центральные процессорные устройства некоторых суперкомпьютеров даже сегодня представляют собой сложные комплексы, построенные на основе микросхем большой и сверхбольшой степени интеграции.

Переход к микропроцессорам позволил потом создать персональные компьютеры, которые проникли почти в каждый дом.

Первым общедоступным микропроцессором был 4-разрядный Intel 4004, представленный 15 ноября 1971 года корпорацией Intel. Он содержал 2300 транзисторов, работал на тактовой частоте 92,6 кГц и стоил 300 долларов.

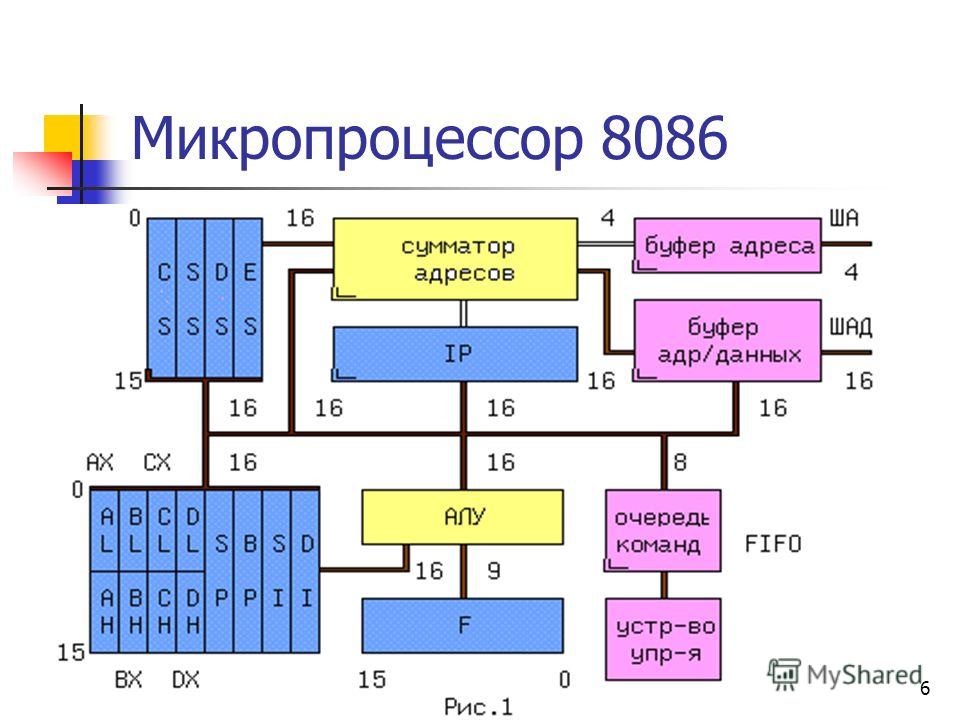

Далее его сменили 8-разрядный Intel 8080 и 16-разрядный 8086, заложившие основы архитектуры всех современных настольных процессоров. Из-за распространённости 8-разрядных модулей памяти был выпущен дешёвый 8088, упрощенная версия 8086 с 8-разрядной шиной данных.

Затем последовала его модификация, 80186.

В процессоре 80286 появился защищённый режим с 24-битной адресацией, позволявший использовать до 16 Мб памяти.

Процессор Intel 80386 появился в 1985 году и привнёс улучшенный защищённый режим, 32-битную адресацию, позволившую использовать до 4 Гб оперативной памяти и поддержку механизма виртуальной памяти. Эта линейка процессоров построена на регистровой вычислительной модели.

Параллельно развиваются микропроцессоры, взявшие за основу стековую вычислительную модель.

За годы существования микропроцессоров было разработано множество различных их архитектур. Многие из них (в дополненном и усовершенствованном виде) используются и поныне. Например, Intel x86, развившаяся вначале в 32-битную IA-32, а позже в 64-битную x86-64 (которая у Intel называется EM64T). Процессоры архитектуры x86 вначале использовались только в персональных компьютерах компании IBM (IBM PC), но в настоящее время всё более активно используются во всех областях компьютерной индустрии, от суперкомпьютеров до встраиваемых решений. Также можно перечислить такие архитектуры, как Alpha, POWER, SPARC, PA-RISC, MIPS (RISC-архитектуры) и IA-64 (EPIC-архитектура).

В современных компьютерах процессоры выполнены в виде компактного модуля (размерами около 5×5×0,3 см), вставляющегося в ZIF-сокет (AMD) или на подпружинивающую конструкцию — LGA (Intel). Особенностью разъёма LGA является то, что выводы перенесены с корпуса процессора на сам разъём — socket, находящийся на материнской плате. Большая часть современных процессоров реализована в виде одного полупроводникового кристалла, содержащего миллионы, а с недавнего времени даже миллиарды транзисторов.

2 Алгоритм работы процессора

2.1 Устройство процессора

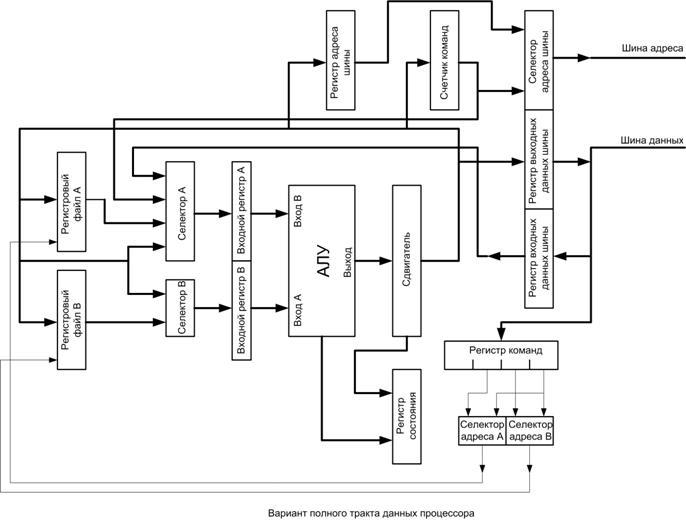

Основные функциональные компоненты процессора

Ядро: Сердце современного процессора — исполняющий модуль. Pentium имеет два параллельных целочисленных потока, позволяющих читать, интерпретировать, выполнять и отправлять две инструкции одновременно.

Предсказатель ветвлений: Модуль предсказания ветвлений пытается угадать, какая последовательность будет выполняться каждый раз когда программа содержит условный переход, так чтобы устройства предварительной выборки и декодирования получали бы инструкции готовыми предварительно.

Блок плавающей точки. Третий выполняющий модуль внутри Pentium, выполняющий нецелочисленные вычисления

Первичный кэш: Pentium имеет два внутричиповых кэша по 8kb, по одному для данных и инструкций, которые намного быстрее большего внешнего вторичного кэша.

Шинный интерфейс: принимает смесь кода и данных в CPU, разделяет их до готовности к использованию, и вновь соединяет, отправляя наружу.

Рис. 1 Внутреннее строение процессора

Все элементы процессора синхронизируются с использованием частоты часов, которые определяют скорость выполнения операций. Самые первые процессоры работали на частоте 100kHz, сегодня рядовая частота процессора — 2000MHz, иначе говоря, часики тикают 2000 миллионов раз в секунду, а каждый тик влечет за собой выполнение многих действий. Счетчик Команд (PC) — внутренний указатель, содержащий адрес следующей выполняемой команды. Когда приходит время для ее исполнения, Управляющий Модуль помещает инструкцию из памяти в регистр инструкций (IR). В то же самое время Счетчик команд увеличивается, так чтобы указывать на последующую инструкцию, а процессор выполняет инструкцию в IR. Некоторые инструкции управляют самим Управляющим Модулем, так если инструкция гласит ‘перейти на адрес 2749’, величина 2749 записывается в Счетчик Команд, чтобы процессор выполнял эту инструкцию следующей.

Многие инструкции задействуют Арифметико-логическое Устройство (АЛУ), работающее совместно с Регистрами Общего Назначения — место для временного хранения, которое может загружать и выгружать данные из памяти. Типичной инструкцией АЛУ может служить добавление содержимого ячейки памяти к регистру общего назначения. АЛУ также устанавливает биты Регистра Состояний (Statusregister — SR) при выполнении инструкций для хранения информации о ее результате. Например, SR имеет биты, указывающие на нулевой результат, переполнение, перенос и так далее. Модуль Управления использует информацию в SR для выполнения условных операций, таких как ‘перейти по адресу 7410 если выполнение предыдущей инструкции вызвало переполнение’.

Это почти все что касается самого общего рассказа о процессорах — почти любая операция может быть выполнена последовательностью простых инструкций, подобных описанным.

2.2 Алгоритм работы процессора

Весь алгоритм работы процессора можно описать в трех строчках

НЦ

| чтение команды из памяти по адресу, записанному в СК

| увеличение СК на длину прочитанной команды

| выполнение прочитанной команды

КЦ

Однако для полного представления необходимо определить логические схемы выполнения тех или иных команд, вычисления величин, а это уже функции Арифметико-логического Устройства.

Арифметико-логическое устройство (АЛУ)— блок процессора, который под управлением устройства управления (УУ) служит для выполнения арифметических и логических преобразований (начиная от элементарных) над данными, называемыми в этом случае операндами. Разрядность операндов обычно называют размером или длиной машинного слова.

2.3 Прерывания процессора

При работе процессорной системы могут возникать особые случаи, когда процессор вынужден прерывать работу текущей программы и переходить к обработке этого особого случая, более срочного и важного. Причинами прерывания текущей программы может быть:

внешний сигнал по шине управления — маскируемых прерываний и немаскируемого прерывания;

аномальная ситуация, сложившаяся при выполнении команды программы и препятствующую ее дальнейшему выполнению;

находящаяся в программе команда прерывания.

Первая из указанных выше причин относится к аппаратным прерываниям, а две другие — к программным прерываниям. Отметим, что аппаратные прерывания непредсказуемы и могут возникать в любые моменты времени.

С помощью аппаратных прерываний осуществляется взаимодействие процессора с устройствами ввода-вывода ( клавиатурой, диском, модемом и т.п.), таймером и внутренними часами, сообщается о возникновении ошибки на шине или в памяти, об аварийном выключении сети и т.п. При возникновении аппаратного прерывания процессор выявляет его источник, сохраняет минимальный контекст текущей программы (включая адрес возврата), и переключается на специальную программу — обработчик прерывания ( interrupthandler). Эта программа правильно реагирует на возникшую ситуацию (например, помещает символ с клавиатуры в буфер, считывает сектор с диска и т.п.), что называется 1обслуживанием прерывания. После обслуживания прерывания процессор возвращается к прерванной программе, как будто прерываний не было.

Программные прерывания обычно называются особыми случаями, или исключениями (exception). Особые случаи возникают, например, при делении на ноль, нарушения при защите по привилегиям, превышении длины сегмента, выходе за границу массива. Как правило, предсказать эти исключения невозможно. Однако встречающаяся в программе 1команда прерывания вполне предсказуема и находится под управлением программиста. Реакция процессора на программное прерывание такое же, как и на аппаратное прерывание, однако его обработка производится 1обработчиком особого случая (exceptionhandler).

Все особые случаи квалифицируются на:

Нарушение(fault). Особый случай, который процессор может обнаружить до возникновения фактической ошибки (например — нарушение правил привилегий). После обработки нарушения можно продолжить программу, осуществив повторное выполнение (рестарт) виноватой команды. Иногда это исключение называют отказом.

Ловушка(trap). Особый случай, который возникает после окончания виноватой программы. После обслуживания ловушки процессор продолжает выполнение программы с команды, находящейся после виноватой. Типичный пример — команда прерывания INT n в процессорах семейства x86 или прерывание при переполнении.

Авария(abort) — возникает при столь серьезной ошибке, что контекст программы теряется и продолжать ее невозможно. Причину аварии установить нельзя, поэтому рестарт невозможен и ее необходимо прекратить. Иногда авария называется выходом из процесса.

Обработка всех прерывания и особых случаев происходит, в общем, одинаково и состоит из двух основных этапов. На первом этапе процессор выполняет некоторые «рефлексивные» операции, которые одинаковы для всех прерываний и исключений, и которыми программист управлять не может. На втором этапе запускается созданный программистом обработчик прерывания или исключения. Все служебные действия процессор производит автоматически.

3 Моделирование работы процессора

Разгон компьютеров — процесс увеличения тактовой частоты (и напряжения) компонента компьютера сверх штатных режимов с целью увеличения скорости его работы. Повышение частоты может достигать максимального значения, при котором сохраняется стабильность работы системы в необходимом для пользователя режиме. При разгоне повышается тепловыделение, энергопотребление, шум, уменьшается рабочий ресурс.

Конечная цель разгона — повышение производительности оборудования. Побочными эффектами могут быть повышение шума и тепловыделения, нестабильности, особенно при условии несоблюдения правил, подразумевающих усиление охлаждающего оборудования, улучшения питания компонентов, тонкой настройки разгона.

Противоположную цель ставит андерклокинг — снизить частоту работы оборудования (и, иногда, необходимого для неё напряжения) и этим достичь снижения тепловыделения, шума, а иногда и нестабильности. Может быть особенно актуальным для тихих помещений, экономии энергии или заряда батареи.

Могут быть разогнана центральные процессоры, память, видеокарты, матплаты, роутеры и прочее.

Классическим методом разгона может быть задание параметров через интерфейс BIOS оборудования и установку там более высоких значений частот работы компонентов системы, нежели штатные. Другой метод — перепрошивка BIOS’а альтернативной от штатной микропрограммой, имеющей уже другие параметры частот и напряжения по умолчанию. Третий метод — повышение частот через операционную систему с помощью специального разгонного программного обеспечения.

Для улучшения охлаждения и снижения уровня шума ставят жидкостное охлаждение, более эффективные и не всегда менее шумные вентиляторы взамен штатных, меняют термопасту, ставят более производительные кулеры. Некоторые типы центральных процессоров подвергаются конструктивной доработке с целью снижения теплового сопротивления между кристаллом и кулером путём удаления защитной крышки процессора и замены термопасты на более новую или на жидкий металл, но уже в самом процессоре, иногда может встречаться припой, который превосходит термопасту по теплопроводности («скальпирование»). Для проверки стабильности используется программное обеспечение, приводящее оборудование в предельный режим нагрузки в тот момент, когда оно уже работает на повышенных частотах.

Для тестов стабильности компонентов компьютеров используются программное обеспечение такое как: Prime95, AIDA64, Super PI, LINPACK, SiSoft Sandra, BOINC, Memtest86+, OCCT.

Заключение

Переход на новые технологии изготовления процессоров, разработка новых алгоритмов их работы является перспективным продвижением данной отрасли. По прогнозам ученых скорость процессоров через 10 лет может достичь 20-ти кратного увеличения по сравнению с современными процессорами.

Автоматизм работы процессора, возможность выполнения длинных последовательных команд без участия человека – одна из основных отличительных особенностей ЭВМ как универсальной машины по обработке информации.

Список источников

https://www.bestreferat.ru/referat-61622.html

https://ru.wikipedia.org/wiki/%D0%A6%D0%B5%D0%BD%D1%82%D1%80%D0%B0%D0%BB%D1%8C%D0%BD%D1%8B%D0%B9_%D0%BF%D1%80%D0%BE%D1%86%D0%B5%D1%81%D1%81%D0%BE%D1%80

https://ru.wikipedia.org/wiki/%D0%A0%D0%B0%D0%B7%D0%B3%D0%BE%D0%BD_%D0%BA%D0%BE%D0%BC%D0%BF%D1%8C%D1%8E%D1%82%D0%B5%D1%80%D0%BE%D0%B2

Алгоритм увеличения вычислительной производительности и баланса загрузки процессоров для моделирования общей циркуляции атмосферы Текст научной статьи по специальности «Математика»

УДК 551.513

Алгоритм увеличения вычислительной производительности и баланса загрузки процессоров для моделирования общей циркуляции атмосферы

© В.П. Пархоменко

Вычислительный центр им. А. А. Дородницына ФИЦ ИУ РАН Москва, 119333, Россия

Представлен анализ некоторых факторов, влияющих на выполнение параллельной реализации модели общей циркуляции атмосферы на многопроцессорной электронно-вычислительной машине кластерного типа. Рассмотрены несколько модификаций первоначального параллельного кода этой модели, направленных на улучшение его вычислительной эффективности, баланса загрузки процессоров. Осуществлена модификация численной схемы по времени модели общей циркуляции атмосферы для возможности осуществления параллельных расчетов блоков динамики и физики. Предлагаемая процедура используется вместе с процедурами распараллеливания блоков динамики и физики на основе декомпозиции расчетной области, что позволяет оптимизировать загрузку процессоров и повысить эффективность распараллеливания. Результаты применения схемы баланса загрузки блока физики рассмотренной модели дают возможность усложнения блока физики без увеличения общего времени счета. Приведены результаты численных экспериментов.

Ключевые слова: модель общей циркуляции атмосферы, особенности параллельной реализации, численные эксперименты.

Введение. Климат [1] является одним из основных природных ресурсов, определяющих последствия для экономики, сельского хозяйства, энергетики, демографии и т. д. Результаты исследований в области климата [2] позволяют предположить, что деятельность человека — важный климатический фактор, и последствия антропогенного воздействия на климатическую систему в ближайшие десятилетия могут быть весьма существенными. Много неопределенностей остается относительно сведений об изменениях климата, особенно в региональном масштабе. Кроме того, крайне неблагоприятные социально-экономические последствия регионального и даже глобального масштаба могут быть вызваны естественными климатическими колебаниями.

Необходима разработка научных основ и системы мер по ограничению негативных последствий экономической деятельности на окружающую среду для сохранения энергии и ресурсов, реструктуризации экономики и адаптации к новым природным и климатическим условиям. Такие основы могут быть разработаны только при совместном изучении глобальных экологических изменений и климата, что позволит осуществить переход к устойчивому развитию [3].

Математическое и численное моделирование является мощным инструментом для исследования климатической системы и прогнозирования изменений климата. Современное моделирование осуществляется с помощью мощных программных средств, в том числе отечественных, для решения задач нестационарной газодинамики многокомпонентного газа различными численными методами [4-7]. Грубые оценки показывают, что для расчетов состояния климатической системы на 100 лет на современной однопроцессорной электронно-вычислительной машине (ЭВМ) необходимо от суток до нескольких месяцев в зависимости от сложности и подробности модели. Следовательно, моделирование климата — одна из задач, требующая для своего решения применения многопроцессорных ЭВМ.

Наиболее сложными и адекватными моделями для описания климатической системы являются модели общей циркуляции атмосферы и океана. В настоящее время разработаны многочисленные модели общей циркуляции атмосферы [2], в которых учтены все существенные процессы в атмосфере. Модели достаточно хорошо описывают циркуляцию атмосферы, температурный режим, осадки, поле давлений, облачность и т. д. Однако слабым местом этих моделей является адекватное воспроизведение взаимодействия атмосферы с подстилающей поверхностью, региональных особенностей климата, а также описания облачности и связанных с ней мелкомасштабных конвективных процессов в атмосфере.

Как известно [8], облачно-радиационная обратная связь является одним из важнейших факторов формирования состояния атмосферы. Характерный масштаб циклонических образований составляет несколько сот километров, атмосферных фронтов — десятки километров, отдельных кучевых облаков — порядка одного километра, а микрофизических процессов в облаках — порядка нескольких метров. Масштаб вертикальных конвективных движений во влажной атмосфере колеблется от нескольких сотен метров до десяти километров.

Таким образом, для адекватного описания только крупномасштабных течений в атмосфере необходимы расчетная сетка с горизонтальным шагом порядка 50 км и несколько десятков уровней по вертикали в тропосфере и стратосфере [9] при условии идеального описания подсеточных процессов.

Увеличение мощности ЭВМ является одним из важнейших требований для более надежных результатов, поэтому в работе рассмотрим методы распараллеливания для решения поставленных задач [10].

Описание модели общей циркуляции атмосферы и процедура распараллеливания., Аф), где X — долгота и ф — широта точки.

Здесь я = рз — рт; У — вектор горизонтальной скорости; а = ёа /

/ — параметр Кориолиса; к — вертикальный единичный вектор; Ф — геопотенциал; Г — вектор горизонтальной силы трения на единицу массы воздуха; а — удельный объем.

Термодинамическое уравнение энергии имеет вид:

— (ясрТ ) + У (ясрТУ) + —(тсрТ а )-яаа дt да

дя ,тГ7 — + УУя

дt

= яН, (3)

где ср — удельная теплоемкость сухого воздуха; Т — температура

воздуха; Н — скорость выделения тепла в единице массы воздуха. Уравнения неразрывности и переноса влаги, соответственно:

—+ У(яУ) + —(та ) = 0, (4)

дt 1 ‘ да1 ; W

д д

— (яд ) + У (тдУ ) + —(яда ) = я((, (5)

дt да

где д — отношение смеси водяного пара; (( — скорость генерации влаги в единице массы воздуха.

Уравнения (2)-(5) являются прогностическими (т. е. эволюционными) для определения зависимых переменных V, Т, т и ц. К ним добавляют уравнение состояния:

где Я — газовая постоянная для влажного воздуха. Диагностическое гидростатическое уравнение:

Уравнения дополняют соответствующие граничные условия; таким образом, получается замкнутая динамическая система в о-координатах.сеткой Аракавы [18] в горизонтальном (широта, долгота) направлении с относительно небольшим числом вертикальных слоев (обычно значительно меньше, чем число горизонтальных точек сетки).

Динамический блок состоит из двух главных компонент: фильтрования и собственно конечно-разностных вычислений. Операция фильтрования необходима на каждом временном шаге в областях, близких к полюсам, чтобы гарантировать, что эффективный размер сетки там удовлетворяет условию устойчивости для явной схемы по времени [18]. Операция основана на разложении потоков в ряд Фурье с обрезанием коротковолновой части спектра и существенно использует все точки географической параллели.

а = ЯТ/р,

(6)

(7)

Эо

В параллельной реализации модели используют разбиение по процессорам двумерной сетки в горизонтальной плоскости (метод декомпозиции). Выбор обусловлен тем, что вертикальные процессы сильно связывают точки сетки, что делает распараллеливание менее эффективным в вертикальном направлении, число точек сетки в вертикальном направлении является обычно небольшим. Каждая подобласть в такой сетке — прямоугольная и содержит все точки сетки в вертикальном направлении. В этом случае есть в основном два типа межпроцессорных обменов [19, 20]. Обмены данными между логически соседними процессорами (узлами) необходимы при вычислениях конечных разностей, а удаленные обмены данными — в частности, для осуществления операции спектрального фильтрования.

Соотношение затрат времени главных блоков исходной параллельной программы модели ОЦА при использовании 4*5*9 градусов разрешения, которое содержит 46*72*9 точек, показано в табл. 1.

Таблица 1

Соотношение затрат времени счета основных блоков модели

Число процессоров Динамический блок, % Физический блок, %

1 63 33

8 67 30

16 70 27

Для счета был использован кластер МВС-60001М (256 CPU) (64-разрядные процессоры Intel® Itanium-2® 1,6 ГГц, при двунаправленном обмене данными между двумя вычислительными машинами с использованием протоколов MPI достигается пропускная способность на уровне 450-500 Мбайт/с). Вычислительные модули связаны между собой высокоскоростной коммуникационной сетью Myrinet (пропускная способность 2 Гбит/с), транспортной сетью Gigabit Ethernet и управляющей сетью Fast Ethernet. Коммуникационная сеть Myrinet предназначена для высокоскоростного обмена между вычислительными модулями в ходе вычислений. Программа была реализована также на сервере Вычислительного центра им. А.А. Дороницына Российской академии наук (ВЦ РАН) с общей памятью (двухпроцессорный, четырехъядерный, на базе Intel Xeon DP 5160, частота 3 ГГц, 4 Гбайт оперативной памяти). Были произведены те же измерения для одного, двух и четырех процессов.

Как следует из табл. 1, основная часть вычислительных затрат модели ОЦА связана с блоками динамики и физики с исключенными процедурами ввода-вывода. Эти процедуры выполняются только один раз, тогда как главная часть повторяется многократно по времени и доминирует по затратам времени выполнения. При сравнении

этих двух блоков можно видеть, что динамическая часть занимает основное время счета, особенно при большом количестве узлов. На масштабируемость параллельной программы влияет отношение затрат обменов данными к затратам вычислений и степень несбалансированности загрузки процессоров в программе. Результаты анализа и оценок затрат времени показывают, что затраты спектральной процедуры составляют заметную часть в параллельной программе модели ОЦА, особенно при увеличении числа узлов [20].

Модификация первоначального параллельного кода модели для улучшения его вычислительной эффективности и баланса загрузки процессоров. Как было отмечено выше, в модели ОЦА можно выделить два главных компонента — динамический и физический блоки. Результаты, полученные в физическом блоке, используют в динамическом блоке как внешние источники для вычисления течения.

Подлежащие интегрированию по времени прогностические уравнения (2)-(5) для основных искомых функций (горизонтальных компонент скорости У, температуры т, отношения смеси водяного пара д, переменной я = р8 — рт, определяющей давление р8) можно записать

в точке (/, у) горизонтальной конечно-разностной сетки в виде:

ду

~д7

= В (у) + 3 (у),

где у — любая из основных искомых функций. — окончательное значение у (после учета влияния источников) в момент времени t + At. Совокупность I и II этапов обеспечивает аппроксимацию рассматриваемых уравнений.

Предлагаемый метод распараллеливания предусматривает одновременный расчет вклада физики и динамики на двух группах процессоров, соответственно. Реализация метода требует изменения численной схемы по времени, которое состоит в одновременном расчете динамики и физики на различных группах процессоров с одних и тех же входных данных:

I группа yD = у0 + AtD (у0 ) ;

II группа у5 = у0 + AtS (у0 ).

По окончании циклов получаем значения основных переменных yD на первой и у s на второй группе процессоров на следующем шаге по времени. После этого процессоры обмениваются данными и на каждой из групп процессоров по формуле у1 = уГ1 + у>5 — у0

рассчитывают окончательные значения искомых функций в момент времени t + At. Легко видеть, что при этом достигается аппроксимация уравнений, но понятно, что результаты исходной и модифицированной схем будут отличаться.

В качестве средства реализации распараллеливания использована библиотека MPI. В настоящее время MPI является наиболее распространенным средством распараллеливания, его реализации есть практически на всех современных многопроцессорных вычислительных машинах, что позволяет обеспечить переносимость программы [21].

Исходная программа была модифицирована в соответствии с высказанными выше соображениями. Для проверки корректности метода по модифицированному и старому вариантам программы были проведены модельные расчеты до установления, имеющие одинаковые начальные условия.

Далее на рисунках приведены некоторые результаты сравнения. На рис. 1 показаны зависимости средней температуры и баланса радиации на верхней границе атмосферы от времени для исходной и модифицированной схем. Указанные средние за сутки и по всему

земному шару величины демонстрируют хорошее совпадение результатов, учитывая сильную изменчивость характеристик атмосферы на коротком интервале в одни сутки.

-10

о -11

я

Он

57 И

-12

-13

-14

100 200 300

Время, дни

а

400

100 200 300 400

Время, дни

б

Рис. 1. Средние глобальные температура атмосферы (а) и баланс радиации на верхней границе атмосферы (б)

в зависимости от времени: 1 — для исходной схемы; 2 — для модифицированной схемы

На рис. 2 показаны графики зависимости от широты зональной компоненты скорости и приземной температуры воздуха, осреднен-ных по долготе для января. Анализ демонстрирует очень хорошее

а б

Рис. 2. Зависимость от широты зональной компоненты скорости (а) и средней приземной температуры воздуха (б) для января:

1 — для исходной схемы; 2 — для модифицированной схемы

совпадение температуры для обоих сезонов, скорости имеют отличия в зимний период в областях сильных градиентов.

Отметим общую особенность распределений основных климатических характеристик, рассчитанных по исходной и модифицированной схемам: наибольшие отличия результатов можно наблюдать в средних и высоких широтах в зимний период. По-видимому, это связано с выпадением осадков в виде снега и интенсивными нестационарными конвективными процессами в атмосфере. Отличия в приземных температурах в более чем 90 % ячеек составляют менее 2 °С. Только в двух ячейках зимой в Северном полушарии над материком разница составляет 10 °С. Для зимы в Южном полушарии наблюдается похожая картина: заметные отличия существуют в трех ячейках в Антарктиде.

Отличия в приземном давлении не превышают 15 мбар в нескольких ячейках и в основном составляют менее 5 мбар.

На рис. 3 показаны географические распределения разности температур воздуха для июля на уровнях 400 и 800 мбар соответственно. На уровне 400 мбар отличия не превышают 2 °С везде за исключением одной точки, где составляют 6 °С. На уровне 800 мбар — подобная картина. Можно утверждать, что отличия в результатах более существенны в приземных областях.

Анализ показывает, что результаты расчетов по модифицированной расчетной схеме дают удовлетворительные результаты и возможно ее применение. В нераспараллеленной программе время счета блока физики составляет 38 %, а блока динамики — 62 %. Значит, на распараллеленной программе может быть достигнуто ускорение

120 150 180

90 70 50 30 10 -10 -30 -50

-2-

5?

СгР

-180 -150 -120 -90 -60 -30

180

Рис. 3. Изолинии разностей температуры воздуха на уровне 400 (а) и 800 мбар (б), рассчитанных по исходной и модифицированной схемам (июль)

приблизительно в полтора раза. Предлагаемую процедуру используют вместе с процедурами распараллеливания блоков динамики и физики на основе декомпозиции расчетной области. Здесь можно применить разработки, описанные в работах [10, 11, 20], что позволяет оптимизировать загрузку процессоров и повысить эффективность распараллеливания (рис. 4).

6 8 Ю 12 14 16 Число процессов

Рис. 4. Зависимость ускорения от числа процессоров:

1 — модифицированный метод; 2 — исходный метод

Другая важная возможность применения метода — усложнение блока физики без увеличения общего времени счета. Рассмотрим четыре численных эксперимента А, В, С и Б с тем, чтобы продемонстрировать результаты:

1) А — использована горизонтальная сетка 4*5 градусов, девять вертикальных уровней, исходный метод для блока физики;

2) В — горизонтальная сетка 4*2,5 градуса для расчета переменных в блоке физики, девять вертикальных уровней;

3) С — горизонтальная сетка 4*2,5 градуса для расчета переменных и 18 вертикальных уровней для радиационных и гидрологических переменных в блоке физики;

4) Б — как в эксперименте С, но в два раза больше спектральных уровней в радиационной модели.

В блоке динамики во всех экспериментах использована фиксированная горизонтальная сетка 4*5 градусов.

В табл. 2 показаны использованные распределения количества процессоров между блоками динамики и физики для указанных вариантов расчетов.

Таблица 2

Распределение процессоров для численных экспериментов А, В, С и Б

Эксперимент А В С Б

Общее количество процессоров 16 22 28 34

Процессоры для блока динамики 10 10 10 10

Процессоры для блока физики 6 12 18 24

Преимущества модифицированного метода, как показано далее, очевидны для экспериментов с относительно большим количеством процессоров, когда большое количество обменов данными между процессорами существует в блоке динамики, а в блоке физики эта проблема отсутствует. Такой эффект объясняет замедление исходного метода расчетов (рис. 5, 2) [20]. Количество процессоров, используемых для блока динамики в модифицированном методе, является одинаковым для всех экспериментов, а увеличивающееся количество

Рис 5. Ускорение счета для численных

экспериментов А, В, С и Б: 1 — модифицированный метод; 2 — исходный метод

процессоров, используемых для блока физики, обеспечивает более подробное и точное описание физических процессов в модели в экспериментах А, В, С и Б. Такое преимущество модифицированного метода не сопровождается увеличением времени счета (рис. 5, 1).

На основе описанной модели климата проведены численные эксперименты по прогнозированию изменения климата при увеличении концентрации углекислого газа в атмосфере, вызванного антропогенными факторами. Для сценария роста концентрации CO2, предложенного в SRES ГРСС [2, 21], рост глобальной температуры атмосферы к 2100 г. составит 2,7 °С, увеличение влажности — 11,5 %, уменьшение толщины морского льда — 25 %. Увеличение приземной температуры атмосферы значительнее над материками и в средних широтах и достигнет 5,2 °С в северных областях Евразии (рис. 6). В Южном полушарии потепление не превысит 2 °С.

А2 С02 всеп еЫв1: Ьиг всЫу = 15 Бскуг = 2100

-260 -220 -180 -140 -100 -60 -20 20 60 100

Долгота

Рис. 6. Изменения температуры воздуха, сценарий А2 С02 (январь)

Существенно изменяется структура меридионального потока воды в Атлантическом океане при реализации рассматриваемого сценария роста концентрации С02. На рис. 7 представлена вертикальная структура среднего меридионального потока в Атлантическом океане для современных условий (а) и прогноз для 2100 г. при реализации сценария роста С02 (б). Наблюдается существенное уменьшение потока максимально на 27 % , что означает уменьшение потока теплых масс воды из экваториальной зоны в северные области Атлантики.

ОРБ! АН Ь А2 С02 всел

Рис. 7. Средний меридиональный поток воды в Атлантическом океане для современных условий (а) и прогноз на 2100 г. (б): ЮП — Южный полюс, Экв — экватор, СП — Северный полюс

Заключение. Рассмотрены результаты применения вариантов параллельного алгоритма климатической модели для различных способов разбиения расчетной области с модифицированными коммуникационными процедурами для обменов информацией между процессорами в параллельном варианте модели общей циркуляции атмосферы. Реализована параллельная программа для различных способов разбиения расчетной области по процессорам в климатической модели.

Представлен анализ некоторых факторов, влияющих на выполнение параллельной реализации модели ОЦА на многопроцессорной ЭВМ кластерного типа. Рассмотрено несколько модификаций первоначального параллельного кода модели, направленных на улучшение его вычислительной эффективности, баланса загрузки процессоров.

Предложен модифицированный метод распараллеливания с одновременным расчетом вклада физики и динамики соответственно на двух группах процессоров с одних и тех же входных данных. Отмечено, что реализация метода требует изменения численной схемы по времени. По модифицированному и исходному вариантам программы проведены модельные расчеты, подтвердившие корректность этого метода. Исследована эффективность модифицированной схемы, при этом повышение точности расчета вклада физики не сопровож-

дается увеличением времени счета. Представлены результаты по моделированию прогнозов изменения климата при увеличении концентрации углекислого газа в атмосфере.

Работа выполнена при поддержке Проектов РФФИ № 14-01-00308, № 14-07-00037, № 16-01-0466.

ЛИТЕРАТУРА

[1] Монин А.С. Введение в теорию климата. Ленинград, Гидрометеоиздат, 1982, 296 с.

[2] Climate Change 2013. The Physical Science Basis. The Physical Science Basis. New York, Cambridge University Press, 2013. Available at: http://www.climatechange2013.org/images/report/WG1 AR5_ALL_FINAL.pdf

[3] Моисеев Н.Н., Александров В.В., Тарко А.М. Человек и биосфера. Москва, Наука, 1985, 272 с.

[4] Dimitrienko Yu.I., Koryakov M.N., Zakharov A.A. Computational Modeling of Conjugated Aerodynamic and Thermomechanical Processes in Composite Structures of High-speed Aircraft. Applied Mathematical Sciences, 2015, vol. 9, no. 98, pp. 4873-4880. http://dx.doi.org/10.12988/ams.2015.55405

[5] Димитриенко Ю.И., Коряков М.Н., Захаров А.А. Применение метода RKDG для численного решения трехмерных уравнений газовой динамики на неструктурированных сетках. Математическое моделирование и численные методы, 2015, № 4, с. 75-91.

[6] Dimitrienko Yu.I., Koryakov M.N., Zakharov A.A. Application of Finite Difference TVD Methods in Hypersonic Aerodynamics. Finite Difference Methods, Theory and Applications. Lecture Notes in Computer Science, 2015, vol. 9045, pp. 161-168. DOI 10.1007/978-3-319-20239-6_15

[7] Димитриенко Ю.И., Захаров А.А., Коряков М.Н., Сыздыков Е.К. Моделирование сопряженных процессов аэрогазодинамики и теплообмена на поверхности теплозащиты перспективных гиперзвуковых летательных аппаратов. Известия высших учебных заведений. Машиностроение, 2014, № 3, с. 23-34.

[8] National Aeronautics and Space Administration: Earth Systems Science: A Closer View. Report of the Earth Systems Science Committee NASA Advisor Council NASA. Washington, NASA, 1988, 208 p.

[9] Белов П.Н., Борисенков Е.П., Панин Б.Д. Численные методы прогноза погоды. Ленинград, Гидрометеоиздат, 1989, 375 с.

[10] Parkhomenko V.P., Lang T.V. Improved computing performance and load balancing of atmospheric general circulation model. Journal of Computer Science and Cybernetics, 2013, vol. 29, no. 2, pp. 138-148.

[11] Пархоменко В.П. Реализация глобальной климатической модели на многопроцессорной ЭВМ кластерного типа. Параллельные вычислительные технологии. Труды Международной научной конференции «Параллельные вычислительные технологии 2009» (Нижний Новгород, 30 марта — 3 апреля 2009 г.). Челябинск, изд-во ЮУрГУ, 2009, 839 с.

[12] Пархоменко В.П. Модель климата с учетом глубинной циркуляции Мирового океана. Вестник МГТУ им. Н.Э. Баумана. Сер. Естественные науки, 2011, спец. вып. «Математическое моделирование», с. 186-200.

[13] Пархоменко В.П. Глобальная модель климата с описанием термохалин-ной циркуляции Мирового океана. Математическое моделирование и численные методы, 2015, № 1, 94-108.

[14] Пархоменко В.П. Моделирование стабилизации глобального климата управляемыми выбросами стратосферного аэрозоля. Математическое моделирование и численные методы, 2014, № 2, c. 115-126.

[15] Пархоменко В.П. Численные эксперименты на глобальной гидродинамической модели по оценке чувствительности и устойчивости климата. Инженерный журнал: наука и инновации, 2012, № 2.

DOI 10.18698/2308-6033-2012-2-45

[16] Пархоменко В.П. Квазислучайный подход для определения оптимальных наборов значений параметров климатической модели. Инженерный журнал: наука и инновации, 2013, № 9. DOI 10.18698/2308-6033-2013-9-962

[17] Parkhomenko V.P. Sea Ice Cover Sensitivity Analysis in Global Climate Model. Research Activities in Atmospheric and Oceanic Modelling. Geneva, World Meteorological Organization, 2003, vol. 33, pp. 7.19-7.20.

[18] Arakawa A., Lamb V. Computational Design of the Basic Dynamical Processes of the UCLA General Circulation Model. Methods in Computational Physics, 1977, vol. 17, pp. 174-207.

[19] Пархоменко В.П. Проблемы реализации и функционирования глобальной климатической модели на параллельных вычислительных системах. Труды IV Международной конференции «Параллельные вычисления и задачи управления» (Москва, 27-29 окт. 2008 г.). Москва, Институт проблем управления им. В.А. Трапезникова РАН, 2008, с. 122-141.

[20] Воеводин В.В., Воеводин Вл.В. Параллельные вычисления. Санкт-Петербург, БХВ-Петербург, 2002, 608 с.

[21] Climate Change 2007: The physical Science Basis. Contribution of Working Group I to the Fourth Assessment Report of the Intergovernmental Panel Climate Change, Paris, 2007, 989 p.

Статья поступила в редакцию 09.09.2016

Ссылку на эту статью просим оформлять следующим образом:

Пархоменко В.П. Алгоритм увеличения вычислительной производительности и баланса загрузки процессоров для моделирования общей циркуляции атмосферы. Математическое моделирование и численные методы, 2016, № 3 (11), с. 93-109.

Пархоменко Валерий Павлович окончил физический факультет МГУ им. М.В. Ломоносова. Канд. физ.-мат. наук, заведующий сектором моделирования климатических и биосферных процессов Вычислительного центра им. А.А. Дородницына РАН Федерального исследовательского центра «Информатика и управление» РАН, доцент МГТУ им. Н.Э. Баумана. Автор более 120 научных публикаций. Область научных интересов: нестационарная газовая динамика, численные методы динамики сплошных сред, математическое моделирование климата. e-mail: [email protected]

Algorithm for computational performance improvement and processor load balancing to simulate the general atmosphere circulation

© V.P. Parkhomenko

Dorodnicyn Computing Centre of RAS, Moscow, 119333, Russia

The paper analyzes some factors affecting the parallel implementation performance of the atmospheric general circulation model designed on a cluster type multiprocessor computer. It considers several modifications of the initial parallel code of this model in order to improve both its computational efficiency and processor load balancing. The

numerical scheme is modified according to the time of the atmospheric general circulation model for parallel computing of dynamics and physics blocks. The proposed procedure is used along with the procedures of paralleling the dynamics and physics blocks based on decomposition of the computational domain. It allows both optimizing the processor load balancing and increasing the paralleling efficiency. The data obtained while using the scheme for the physics block load balancing allow for complication of the physics block without increasing the total computational time. The results of numerical experiments are given.

Keywords: atmospheric general circulation model, parallel implementation features, numerical experiments.

REFERENCES

[1] Monin A.S. Vvedenie v teoriyu klimata [Introduction to the theory of climate]. Leningrad, Gidrometeoizdat Publ., 1982, 296 p.

[2] Climate Change 2013. The Physical Science Basis. The Physical Science Basis. New York, Cambridge University Press, 2013. Available at: http://www.climatechange2013.org/images/report/WG1AR5_ALL_FINAL.pdf

[3] Moiseev N.N., Aleksandrov V.V., Tarko A.M. Chelovek i biosfera [Man and the biosphere]. Moscow, Nauka Publ., 1985, 272 p.

[4] Dimitrienko Yu.I., Koryakov M.N., Zakharov A.A. Applied Mathematical Sciences,, 2015, vol. 9, no. 98, pp. 4873-4880. http://dx.doi.org/10.12988/ams.2015.55405

[5] Dimitrienko Yu.I., Koryakov M.N., Zakharov A.A. Matematicheskoe mo-delirovanie i chislennye metody — Mathematical Modelling and Computational Methods, 2015, no. 4, pp. 75-91.

[6] Dimitrienko Yu.I., Koryakov M.N., Zakharov A.A. Finite Difference Methods, Theory and Applications. Lecture Notes in Computer Science, 2015, vol. 9045, pp. 161-168. DOI 10.1007/978-3-319-20239-6_15